芯片资讯

热点资讯

- FPGA系列之“速度等级”选型介绍

- 2023年全球半导体Top10榜单生变:Intel夺回第一,NVIDIA跻身前五

- 注册资金1.8亿元,4家国产半导体设备商携手成立合资公司!

- 瑞萨电子(RENESAS)的起源:日本三大电子巨头的半导体根基!

- 莱迪思:小型低功耗FPGA器件,迎接AI、嵌入式视觉的爆发

- 亿配芯城为大家介绍博通 (Broadcom) 芯片产品系列及料号解析

- 维信诺美国公司启动运营,2023年第三季度营收达14.26亿元

- 亿配芯城接入DEEPSEEK AI 大模型,让芯片采购更灵活

- 芯片供应链在人工智能和电子制造中的重要角色

- 电子工程师必备:Marvell(美满电子)产品线与料号解码,从型号到应用

- 发布日期:2024-01-15 13:00 点击次数:155

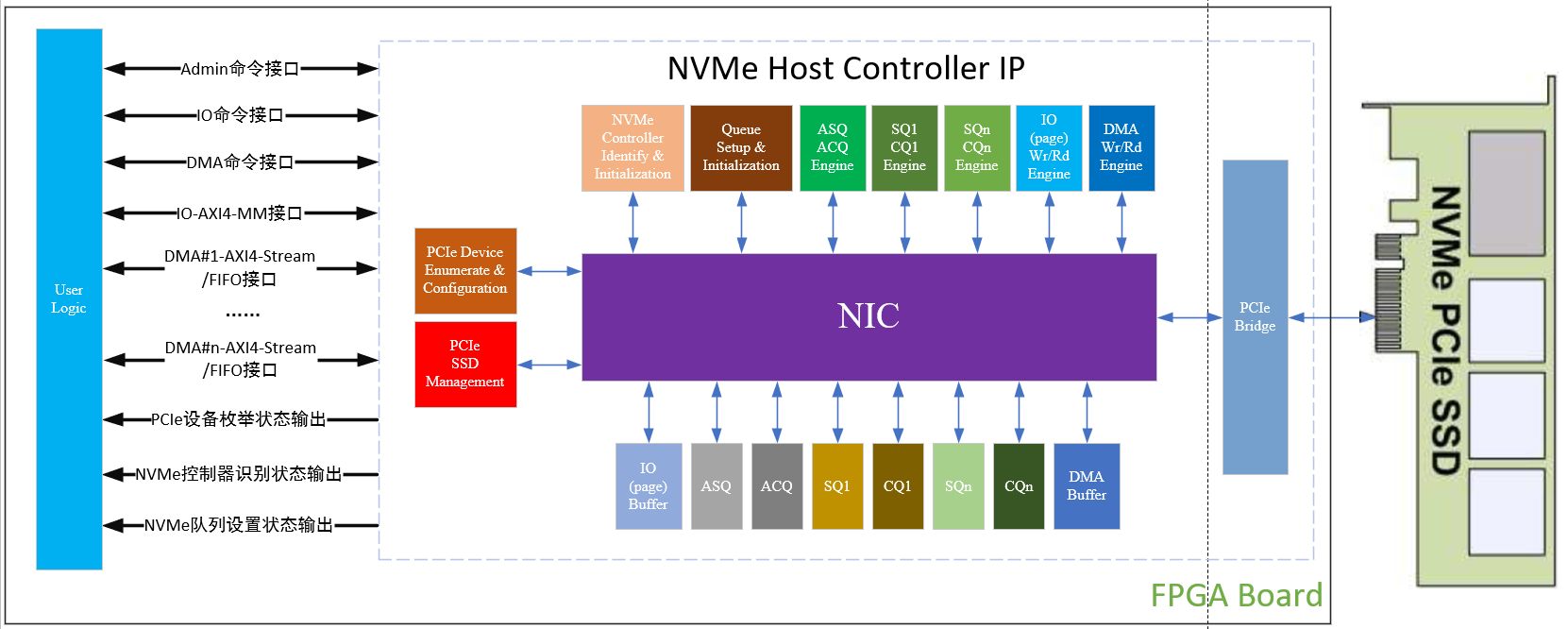

NVMe Host Controller IP

介绍

NVMe Host Controller IP可以连接高速存储PCIe SSD,无需CPU和外部存储器,自动加速处理所有的NVMe协议命令,具备独立的数据写入AXI4-Stream/FIFO接口和数据读取AXI4-Stream/FIFO接口,非常适合于超高容量和超高性能的应用。此外,NVMe Host Controller IP支持RAID存储,从而可实现更高存储性能和存储容量。

无需CPU,NVMe Host Controller IP自动执行对PCIe SSD的PCIe设备枚举和配置、NVMe控制器识别和初始化、NVMe队列设置和初始化,实现必须以及可选的NVMe Admin Command Set和NVM Command Set,实现对PCIe SSD的复位/断电管理、IO(Page)读写、DMA读写和数据擦除功能,提供用户一个简单高效的接口实现高性能存储解决方案。

针对多通路访问PCIe SSD,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级机制实现多个DMA通道对同一块PCIe SSD的高效访问,从而达到多通道访问的并行需求和QoS要求。

特性

支持Ultrascale+,Ultrascale,7 Series FPGA

支持PCIe Gen4,PCIe Gen3,PCIe Gen2 SSD

无需CPU和外部存储器

自动实现对PCIe SSD的PCIe设备枚举、NVMe控制器识别和NVMe队列设置

支持对PCIe SSD的NVM Subsystem Reset、Controller Reset和Shutdown

支持NVMe Admin Command Set:Identify、SMART、Create/Delete IO Submission/Completion Queue、Set Feature

支持NVMe NVM Command Set:Write、Read、Flush、Dataset Management

提供1个Admin命令接口,实现对PCIe SSD的复位/断电管理功能

提供1个IO命令接口,实现对PCIe SSD的IO(Page)读写、Cache Flush和逻辑数据块擦除功能;提供1个IO-AXI4-MM接口读写IO(page)数据

提供1个DMA命令接口,实现对PCIe SSD的DMA读写功能;提供1个DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口实现DMA数据的输入和输出

针对多通路DMA需求, 芯片采购平台可以配置N个DMA命令接口和N个DMA-AXI4-Stream-In/Out或DMA-FIFO-In/Out接口

支持的NVMe设备:

Base Class Code:01h(mass storage),Sub Class Code:08h(Non-volatile),Programming Interface:02h(NVMHCI)

MPSMIN(Memory Page Size Minimum):0(4K-byte)

LBA Unit:512-byte,1024-byte,2048-byte或4096-byte

一个NVMe Host Controller IP直接连接到PCIe SSD

易于集成的同步、可综合Verilog设计

通过完全验证的NVMe Host Controller IP

概述

NVMe Host Controller IP作为一个对PCIe SSD的高性能存储控制器,不但提供对PCIe SSD的配置管理功能,而且提供对PCIe SSD的IO(Page)读写以及DMA读写功能。

NVMe Host Controller IP具备PCIe SSD Manegement,实现对PCIe SSD的复位/断电管理功能。

NVMe Host Controller IP具备ASQ/ACQ引擎,实现NVMe Admin Command Set:Identify、SMART、Create/Delete IO Submission/Completion Queue、Set Feature。

NVMe Host Controller IP具备IO(Page) Wr/Rd引擎和SQ1/CQ1引擎,实现对PCIe SSD的IO(Page)读写、Cache Flush和逻辑数据块擦除功能。

NVMe Host Controller IP具备DMA Wr/Rd引擎和SQn/CQn引擎,实现对PCIe SSD的DMA读写功能。

上电后,NVMe Host Controller IP内置的PCIe Device Enumerate & Configuration自动实现对PCIe SSD的PCIe设备枚举和配置;然后内置的NVMe Controller Identify & Initialization自动实现对PCIe SSD的NVMe控制器识别和初始化;最后内置的Queue Setup & Initialization自动实现对PCIe SSD的NVMe队列设置和初始化。上电后至此,NVMe Host Controller IP完成对PCIe SSD的所有配置和初始化工作,可以开始提供对PCIe SSD的读写、擦除、复位操作。

图 2 NVMe Host Controller IP结构框图

产品规格

性能

PCIe配置参数:Max Payload Size=256-byte,Max Read Request Size=512-byte

PCIe Gen3 SSD,1个DMA通道:

DMA写入速度可达3300MB/s

DMA读取速度可达3500MB/s

PCIe Gen2 SSD,1个DMA通道:

DMA写入速度可达1700MB/s

DMA读取速度可达1800MB/s

资源

表3 PCIe Gen3 SSD,1个DMA通道资源

ZU7EV LUTs FFs BRAMs URAM PCIe 资源 23657 33781 40 2 1

交付清单

可交付资料:

1.详细的用户手册

2.设计文件:源代码或网表

3.时序约束

4.测试或Demo工程

5.技术支持:邮件,电话,现场,培训服务

审核编辑:黄飞

- Cyclone系列FPGA:高性能可编程逻辑解决方案的技术解析与应用场景2025-08-25